导语

在前文中,根据WLCSP封装工艺、传输线理论以及电磁场相关理论,已经完成了芯片封装在芯片减薄、芯片划片、Molding、RDL、Bumping的设计和仿真工作,仿真结果显示设计的FanoutWLCSP2P2M封装能够满足项目指标要求。本文将根据前面设计的模型进一步设计制作封装芯片的测试夹具实物,然后对测试夹具进行逐步焊接和调试,再对测试结果进行处理,扣除线缆等影响测试结果的因素,与裸片数据进行对比,最终以验证其射频性能的方式评估封装设计的总体性能是否符合预期目标。

测试夹具的设计与制作

通过上一篇对裸片Die-RDL-Bumping-PCB的级联仿真,封装芯片的最终应用场景就是焊接在PCB电路板上进行应用,并且上一章已经仿真了部分PCB版图。为了验证封装芯片的电气性能是否满足设计要求,必须设计并绘制完整的PCB版图,并将封装芯片测试夹具PCB版图的加工文件交给PCB加工厂进行生产加工,在加工后对PCB进行元器件的贴片焊接就可以用于封装芯片的测试任务。本次设计采用Cadence公司的原理图设计软件Orcad和版图设计软件Allegro进行设计。

依据Cadence公司提供的电子产品设计工具的使用步骤,第一步需要建立元件库,其中元件库中的元件符号代表该元件在原理图中的表现形式,接着按照芯片工作所需要的电路在原理图中将各元器件进行连接,虽然原理图的设计相对轻松,只需要考虑电气连接的正确性而无需顾及布局问题,但是原理图设计得是否合理关乎整个PCB设计的正确性,PCBlayout也是根据原理图的电气连接特性进行设计的。

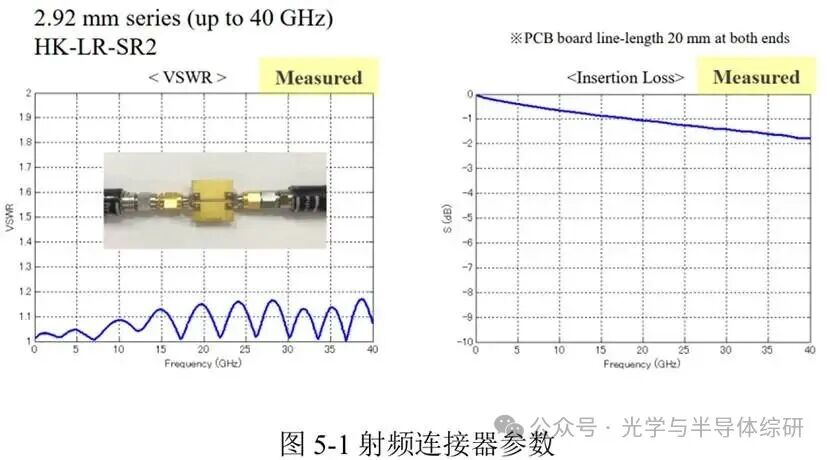

在正式开始PCB设计时,需要根据设计需求来确定板框、安置固定孔以及设计叠层参数。由于该芯片的控制平台和封装芯片的测试板通过排针相连,加上该芯片有8个管脚,因此PCB的板框尺寸被设定为多边形结构。为后续测试考虑,供电接口为香蕉头,控制信号接口为Pitch为2.54mm的20pin排针,用于与FPGA开发板相连,以连接封装芯片里面的数字信号DS1-DS6。射频接口尤为重要,直接影响到芯片的射频性能,经过筛查,选取日本广濑制造的2.92mm压接连接器。图5-1为日本广濑连接器HK-LR-SR2的S参数性能,可以看到实物测试在0GHz40GHz内驻波比均在1.2以下,在10GHz-13GHz内驻波比能达到1.1以下,并且实物尺寸较小,能更好的测试出芯片封装后的性能。

PCB版图的设计是测试电路板实现中的最重要的一步。在正式绘制版图之前,需要绘制好所有元器件的PCB封装库才能在Allegro中进行布局。对于每个电子元器件的尺寸信息,都可以通过查阅相关元器件的规格书,在绘制时封装尺寸和元器件焊盘时需要流出足够的余量,通常使它们的大小比元器件数据手册给出的封装尺寸大一些,一是为了防止PCB在加工过程中的误差出现,二是为了降低在后续贴片的难度和避免贴片时出现虚焊的情况。

在规划电路板叠层时,需全面权衡其大小、电子元器件的大小及电磁兼容度(EMC)等多项因素。虽然多层PCB可以带来更方便的线路布局,但这也会大幅提升生产费用和困难程度。因此,在确定叠层的过程中,使主要信号尽可能靠近地面层,避免跨越分离区域。

表5-1给出了PCB的叠层规划,由表可知整个PCB规划为四层,顶层用于走射频信号,第二层为顶层射频信号提供一个完整的地平面,第三层和第四层为控制信号和电源层。PCB由两块合芯板压合而成,第一块合芯板材料为0.5oz的铜和Roger4350B的介质材料,厚度为0.168mm,相对介电常数为3.66。两块合芯板之间以及第二块合芯板所用介质材料均为FR4,相对介电常数为4.2,在TOP和BOTTOM使用0.5oz的铜厚,但是在加工完后会对表面进行电镀,完成铜厚约0.045mm。

对于PCB设计的核心步骤——布局与布线的规划至关重要;不仅要满足基本功能需求并易于测试使用外,还需要关注诸如电磁干扰(EMI)及电子设备兼容性能(EMC)问题。元件的布局应当便于射频信号的走线,避免信号的串扰,但是对于射频信号,在考虑信号的串扰的同时还应考虑如何走线最短,减少信号的损耗。测试夹具的版图中,为增加射频信号的完整性,所有射频通道都有完整的地孔进行包裹,并且第二层为一块完整地。在布局时,数字信号和射频信号需要留有足够的安全距离,并且分割射频地和数字地以减少信号之间的串扰和耦合,为了方便该芯片后续进行高低温测试,在布局设计时将去耦滤波电容放置在PCB底部,并且尽量靠近芯片的电源管脚提升去耦效果。

布线设计要保证走线之间有一定的安全间距和误差距离,避免信号间的串扰。对于高频信号要减少其走线长度从而减少不必要的损耗。同时,需遵循微带线的特性阻抗要求来设定线宽。通常情况下,会利用ShortcuttoSi9000工具对具体的数值进行计算。至于芯片接口部分的线宽与线距,将采用前述HFSS级联模拟的结果作为参考依据。电源线直接采用铺铜的方式加宽以减少电感效应。在PCB上按照芯片端口设计的线宽线距,设计了一条与芯片输出和输出端口等长的直通微带线,该微带线要求与芯片引出的微带线线宽和线距一致,用于封装芯片测试扣除微带线带来的损耗,使得测试结果更加可靠。

因为该封装芯片后期会进行高低温测试,可以将去芯片周围的耦滤波电容放置在PCB板的背面。结合Cadence和PCB加工厂的布局和布线的规则完成整个测试夹具的设计。

在完成整个布局布线设计后,需要在射频电路的两侧增加3倍线宽的铜皮露出区域,该露铜区域直接与地面连接,以增大地面积,有助于降低地线阻抗,稳定信号传输,从而显著减少电磁辐射干扰,提高PCB的抗干扰性能。在PCB合适的位置需要添加丝印字符,用于说明,便于后期调试。同时需要在顶层和底层放置PCB的光学定位点fiducialmark,又称为光猫,用于表面贴装工艺中的定位PCB板元件。

当PCB的设计过程结束时,需要通过软件自带的DRC(DesignRuleCheck)工具对设计的正确性和制造可行性进行检测,以确保其符合各种工艺规范。一旦经过DRC的审核且没有发现问题,会生成Gerber文件和IPC文件以便于工厂生产,最终PCB版图如图5-2所示。

然后再根据焊接文件和原理图生成的BOM表对版图设计中使用到的各个元器件进行贴片焊接,最终得到可用于测试的封装芯片测试电路板实物如图5-3所示。

测试结果与分析

在封装芯片和测试夹具实物加工完成后,并将封装芯片与周围应用电路进行焊接,还需要逐一调试和优化各个部分以确保电路的正确连接,才能得出封装芯片准确的电气性能。本课题对封装芯片的是主要使用罗德与施瓦茨公司生产的矢量网络分析仪(R&SZNB40)仪器,该仪器能够支持40GHz以下的测试。供电由直流电源IT6332L供电,控制信号由接入PC端的FPGA开发板进行控制,测试环境如图5-4所示。

因为测试环境并非理想,整个测试环境不存在绝对的无误差,封装芯片与测试设备之间的连接存在接头损耗以及线缆本身的损耗,为了准确的测量射频信号的指标,验证封装的可行性,在对封装芯片正式测试之前要对测试环境的线路的损耗进行校准。首先先用校准件对仪器和射频线缆进行校准,再通过测试电路板上专门制作的直通线校准掉微带线带来的损耗,最后再对封装芯片进行测量,尽可能校准掉不必要的损耗。

按照图5-5所示测试框图连接校准件、射频线缆和矢量网络分析仪,使用25dBm作为输入功率,扫描频率为0.05GHz到40GHz,步径为50Mhz,共800个点,刚好符合之前的仿真点数。根据矢网校准界面依次对开路、短路、负载、直通进行校准,使用一个双阴直通接头校准结果如图所示。

根据校准测试结果,如图5-6所示。校准后的插损在0.1dB左右,回波损耗均在-30dB以下,因为是采用一个直通接头进行校准测试,不可能出现完全没有损耗的环境,因此可以确定仪器和射频线缆经过校准,仪器和射频线缆的损耗并不会对封装芯片的性能带来较大影响。经过校准完成后,正式开始测试。在之前设计的PCB板上,设计了一条微带直通线,这条直通线长度等于封装芯片输入端和输出端的微带线长度,可以用于校准PCB上封装芯片两端的微带线损耗,使得测试结果更加准确。微带线测试结果如下:

测试结果如图5-7所示,在0.05GHz-40GHz的范围内回拨损耗S11和S22逐渐恶化,插损也逐渐增加,在25GHz以内回损均在-20dB以下。在芯片工作的频带内,10GHz处的损耗为1.818dB,13GHz处的损耗为2.153dB,回波损耗在均在-26dB以下。

在PCB板上把用于校准损耗的微带传输线测试后,将测试的微带直通线换成芯片的输入和输出口,对封装芯片进行测试,测试结果如图5-8所示。

测试结果经过整理,如图5-8所示,其中1、2端口分别表示矢量网络分析仪的Port1和Port2,也就是芯片的输入和输出端口,对应芯片就是RF端口和OUT端口。芯片的增益S21在10Ghz、12GHz、13GHz处分别为16.464GHz、15.69dB、13.912dB,带内平坦度在3dB以内;输入回波损耗和输出回波损耗均在-13dB以下。

因为芯片的测试是焊接在PCB上进行测试的,有一段PCB微带的损耗,要得到封装芯片准确的测试结果,需要对上面得到的结果进行去嵌处理,就相当于从测试结果中把由于测试夹具带入的测试误差减去,从利用ADS中控件Deembed对测试结果进行处理。

如图5-11所示,SNP3为测试原始数据,去嵌数据SNP4为图中直通微带线的测试数据,去嵌后结果如图5-10所示。

经过去嵌处理后得到了相对准确的封装芯片数据,如图5-10所示,其中3、4端口分别表示矢量网络分析仪的Port1和Port2,也就是芯片的输入和输出端口。在10GHz、12GHz、13GHz频点处,芯片的增益分别为18.182GHz、17.67dB和15.952dB,带内平坦度保持在2.5dB以内;同时输入回波损耗和输出回波损耗均低于-13dB。

上面已经获得了准确的封装芯片测试数据,使用ADS工具分别处理测试原始数据去嵌、裸芯片级联输入端和输出端封装仿真数据,如图5-11所示。

上图5-11中,(3,4)端口为实际封装芯片测试去嵌后的数据,其中SNP3为测试原始数据,SNP4为去嵌数据;(5,6)为裸片测试数据级联输入端封装仿真数据和输出端封装仿真数据,其中SNP6为裸片测试数据、SNP5为输入端封装仿真数据、SNP7为输出端仿真数据。通过ADS的控件,可以将裸片测试数据和芯片封装的前后仿真数据级联起来,数据处理结果如图5-12所示。

根据对比结果图5-12所示,在10GHz-13GHz封装芯片输入回波损耗和输出回波损耗实际测试结果和仿真结果较吻合,包括谐振频点基本一致。输入端回波损耗封装数据比裸片级联封装仿真数据更好一些,输出端回波损耗封装数据比裸片级联封装仿真数据则差一点。在10GHz-12GHz时,封装芯片与裸片级联仿真数据的增益较吻合,但是在12GHz以上,封装芯片测试数据与裸片级联封装仿真数据相差在1dB以上,裸片级联封装仿真数据的增益下降的更快,结合上一章仿真数据基本都在0.2dB以内,这可能与裸片测试不准或芯片间的差异有关。从Smith圆图来看,封装芯片更偏向于感性区,而裸片级联封装仿真数据偏向于容性区。根据数据对比整体而言,封装芯片测试结果比预期更理想。

注:本文节选自电子科技大学论文《基于WLCSP封装的RDL技术的研究》,作者董潇,指导老师王建勋教授。本文仅作技术分享之用,版权归属原作者原发表处。

来源:光学与半导体综研

声明: