Quilter 公司借助人工智能设计出一台功能完备的类 Unix 计算机,将原本需要一个季度的印制电路板(PCB)设计周期压缩至短短一周。

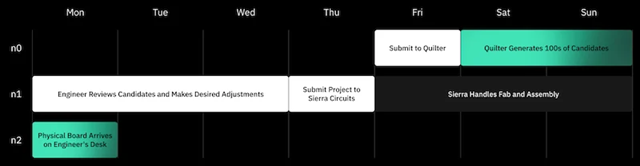

Quilter是一家专注于电子设计物理驱动型人工智能技术的企业,该公司近日发布了“速通计划”(Project Speedrun)。这一项目充分验证了人工智能驱动的设计工具,能够大幅缩短传统 PCB 的研发周期。在演示过程中,一名工程师仅依靠Quilter的物理驱动型人工智能平台,历时不到一周,便完成了一套双板 Linux 计算机从原理图绘制到可投产版图设计的全流程工作。

速通计划

Quilter表示,速通计划打造的计算机,是全球首款由人工智能自主设计的计算机。

该计算机以恩智浦(NXP)i.MX 8M Mini 处理器为核心,整套系统包含两块电路板,集成元器件共计 843 个。在首次开机测试中,设备便成功启动并加载了 Debian 操作系统。传统流程中需要耗费数月的元器件布局、线路布线与设计迭代工作,在该项目中仅需极少人工干预即可完成。

速通计划的核心是Quilter自研的物理驱动型人工智能引擎。该引擎将 PCB 版图设计视作约束优化问题,而非基于规则的自动化任务。在元器件布局与布线阶段,系统会同步评估信号完整性、电源完整性、热特性及电磁耦合情况,而非依赖预设的布局启发算法,或是在布线完成后再进行后期修正。

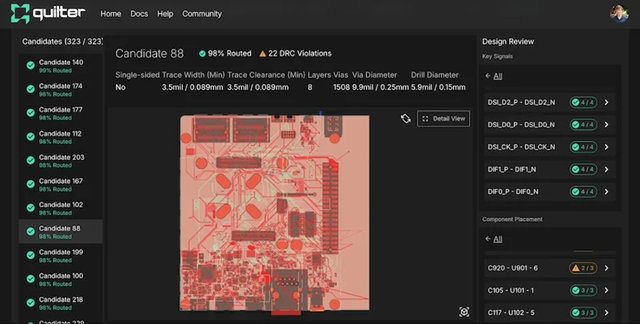

人工智能引擎会筛选出所有可行的设计方案,并以图形用户界面(GUI)形式呈现。

这一机制使得电气约束从版图设计初期,就能对物理层面的设计决策产生影响,而不是等到布线完成后才进行合规性验证。本次验证设计以恩智浦 i.MX 8M Mini 处理器为核心,该处理器兼具高速 DDR 接口、高密度电源分配需求与混合信号外设。最终落地的方案采用双板架构,集成了 843 个元器件,涵盖存储模块、各类接口及配套无源器件。

Quilter的平台可自动完成元器件分组、引出线布线、阻抗受控走线及电源层拓扑设计,同时满足标准制造流程对可制造性的各项约束要求。

本次演示的一大亮点,在于设计过程中人工干预的需求极低。在导入初始原理图并定义设计约束后,人工智能生成的PCB版图仅需经过少量人工审核与微调,即可进入投板环节。在速通计划中,配套的候选方案工具可将大量潜在设计配置,系统性地筛选为数量可控的可行方案集。这些“候选方案” 涵盖了特定的拓扑结构、布线方式与约束条件组合,切实具备满足性能要求的可行性。

演示结果显示,该套电路板首次开机即成功启动 Linux 系统。从工作流程角度来看,速通计划验证了:在PCB版图生成环节直接融入物理特性感知能力,能够减少复杂嵌入式系统的设计迭代次数,提升一次流片成功率。

尽管速通计划证明了人工智能辅助 PCB 设计在缩短研发周期方面的巨大潜力,但也凸显出人类专业经验仍不可或缺的应用场景。对于习惯通过人工方式掌控布局与布线决策的团队而言,将Quilter这类工具整合到现有设计流程中,需要建立一套标准化的应用规范。

使用Quilter平台的工程师,仅耗时 38.5 小时完成了这套双板系统的后期优化工作 —— 其中主板优化耗时 12 小时,而传统人工设计的同类工作预计需要 238 小时;系统级模块(SOM)优化耗时 26.5 小时,传统人工设计则需 190 小时。也就是说,38.5 小时的人工投入,取代了原本预计 428 小时的人工工作量。

随着设计向更高速率领域拓展,这些挑战将愈发凸显。更高的传输速率对应更严苛的时序裕量与先进电源完整性要求,需要研发人员开展严谨的设计评审,并结合领域专属经验做出判断。高速电路设计的难点在于,随着数据速率提升,性能裕量会急剧缩减,导致信号传输路径的容错空间大幅压缩。损耗、串扰、阻抗不连续性及电源完整性等问题,原本属于次要考量因素,如今已成为首要设计约束条件。

在高速场景下,细微的版图设计决策,都可能对眼图张开度、信号抖动及系统整体可靠性产生显著影响。随着“速通计划” 这类人工智能驱动的版图设计工具不断成熟,其长期价值不仅取决于研发效率的提升幅度,更在于能否在适配下一代接口技术的同时,与成熟的验证流程保持兼容。

原文

https://www.allaboutcircuits.com/news/for-the-first-time-ai-designs-computerin-less-than-a-week

欢迎加入 EETOP 微信群