如果将芯片设计比作在微观世界里建造一座超级城市,那么在当今的先进工艺节点下,这座城市的规模已经从“百万人口”激增到了“百亿人口”乃至“千亿人口”。

随着AI大模型、自动驾驶、5G通信等应用场景的爆发,SoC(系统级芯片)的晶体管数量早已突破百亿门级大关。这种指数级的复杂度增长,给验证环节带来了史无前例的挑战:软件仿真跑不动,硬件成本居高不下,上市窗口期(TTM)却被极限压缩。

在这个“验证定生死”的时代,单点工具的突破已无法解决系统级难题。作为国内首家数字EDA供应商,成立二十载的思尔芯(S2C)正在给出一种系统性的解题思路——异构验证方法(Heterogeneous Verification Methodology)。

不仅仅是“原型验证”的代名词,今天的思尔芯已经构建起了一套覆盖架构设计、软件仿真、硬件仿真、原型验证、形式验证到云服务的数字设计全流程EDA平台。特别是其最新披露的工程数据显示,思尔芯已具备支撑上百颗FPGA级联的超大规模验证能力。本文将深入这一工具链的肌理,剖析其如何帮助设计团队穿越数字迷宫。

基石的进化:从“单点”到“百芯级联”的硬实力

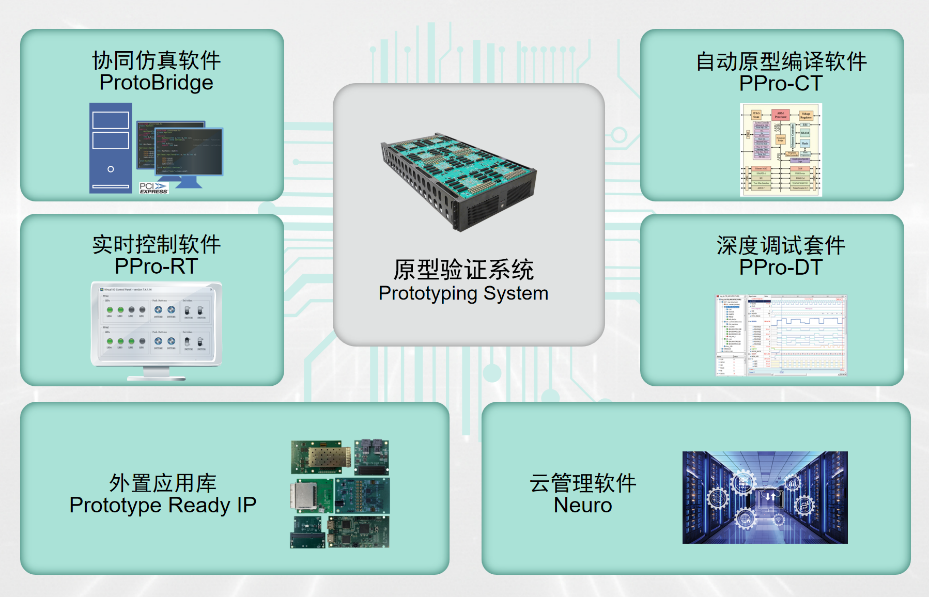

如果说架构设计是“纸上谈兵”的推演,那么原型验证就是“真刀真枪”的演习。作为思尔芯起家的王牌领域,芯神瞳(Prodigy)原型验证逻辑系统在面对超大规模设计时,够充分满足客户对处理系统复杂度、产品稳定性、高效编译以及高性能运行的严苛要求。

芯神瞳(Prodigy)原型验证系统

在百亿门级的设计中,原型验证面临的是“性能”、“可靠性”与“高效编译”。当设计规模大到需要跨越数十甚至上百颗FPGA时,硬件的稳定性往往成为木桶上最短的那块板。

思尔芯的芯神瞳系列给出了工业级的答案。芯神瞳上一代产品Logic Matrix就实现了极高密度的组网部署——仅需2个机柜,即可实现128颗FPGA的超大规模组网。这种高集成度不仅节省了宝贵的实验室空间,更极大地减少了物理连线带来的信号衰减风险。

更令人印象深刻的是其稳定性。在思尔芯 RT工具严谨的操作流程保障下,该套128颗FPGA的超大组网在某客户近两年的高强度使用中,实现了“零差错、零故障”的记录。这标志着国产原型验证工具已经跨越了“能用”的阶段,迈入了“高可靠、工业级”的成熟期。

在开芯院昆明湖16核RISC-V处理器及NoC互联系统的验证中,芯神瞳展现“高性能”与“高效编译”能力。设计被部署至2台S8-100Q (8片VP1902),运行频率为13.3MHz。同时,编译时间大幅缩短。RCF软件先进行RTL代码分割,再并行综合,使得全流程编译周期缩短至17小时。增量综合功能更是保证了每日的版本迭代与更新。

软件的灵魂:RCF与ICF的效率变革

硬件决定了验证的容量上限,而软件则决定了验证的效率下限。面对动辄百亿门的设计,如果没有强大的软件调度,堆砌再多的硬件也只是一盘散沙。思尔芯自主研发的RCF(RTL Compile Flow)与ICF(Incremental Compile Flow)技术,正是驾驭这些庞大硬件的“神经中枢”。

RCF:驾驭上百颗FPGA的“切割艺术”

当一个SoC设计大到无法放入单颗FPGA时,必须进行多片分割(Partitioning),这就像把一张巨大的地图切成碎片拼图,既要切得开,又要拼得准。

思尔芯的RCF技术通过时序与拥塞优化算法,能够全自动处理基于RTL级数据库的大规模分割。最新的落地案例显示,RCF已经成功支撑起一百多颗FPGA规模的原型验证项目,并具备支持更大规模的编译潜力。

除了规模,RCF更强调“速度”。在与某客户的合作项目中,得益于RCF的高效分割与自动化流程,客户实现了惊人的敏捷迭代:从24颗FPGA起步,迅速扩展至32颗、40颗,最终扩展至一百多颗的完整系统。在这个过程中,系统的首次Bring-up(启动调试)仅耗时1周。对于分秒必争的芯片研发团队而言,这种“即插即用”的扩展能力意味着巨大的时间红利。

ICF:分秒必争的“增量编译”

在验证后期,Bug修复往往只涉及几行代码的修改。如果因为这点微小的变动就要重新编译整个百亿门的设计,耗时可能长达数小时甚至更久,这是工程师无法忍受的“垃圾时间”。

ICF技术正是为此而生。它能够智能识别RTL代码中的变动部分,仅对受影响的逻辑块进行增量编译。数据表明,完整编译后,在ICF的加持下效率显著提升,极大地加速了Bug收敛的速度。

顶层设计的智慧:周期左移与架构探索

在夯实了底层的验证能力后,思尔芯敏锐地捕捉到“周期左移”的趋势,主动将防线前移,深入到设计的源头。

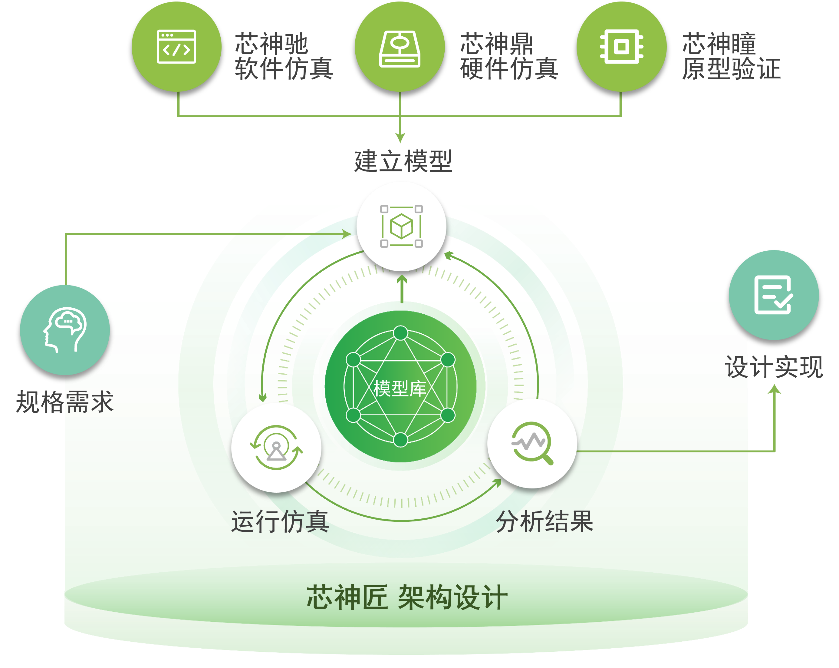

芯神匠(Genesis)架构设计软件的推出,标志着思尔芯从“验证专家”向“全流程专家”的蜕变。在RTL代码尚未成型之前,芯神匠便允许架构师通过建模组件和丰富的标准协议模块,对SoC的性能、功耗进行快速探索与评估。

芯神匠(Genesis)架构设计软件

这不仅避免了后期因架构缺陷导致的推倒重来,更与后续的原型验证形成了联动:芯神匠生成的模型可以直接对接原型验证系统进行仿真加速;也可以和硬件仿真搭建混合仿真系统将既有设计转换为模型,实现“设计即验证”的闭环。

填补鸿沟与全域调试

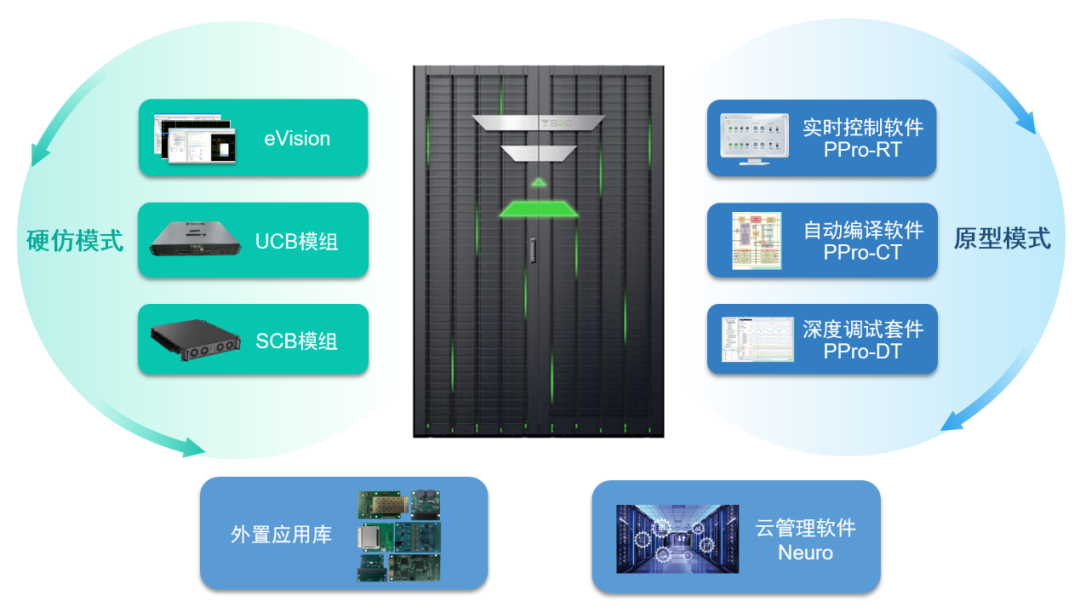

在软件仿真(慢但可视性好)和原型验证(快但可视性弱)之间,思尔芯前几年推出了首款国产企业级硬件仿真系统芯神鼎(OmniArk)来填补空白。思尔芯迭代升级的新一代OmniDrive硬件仿真系统,直指大规模芯片设计的效率瓶颈。作为一款灵活高效的双模式系统,它支持硬件仿真与原型验证两个模式,为用户在不同设计阶段提供高性价比与高效率的选择。

芯神鼎(OmniDrive)硬件仿真系统

芯神觉数字电路调试软件是自研数字电路调试软件,提供一个全面的分析与调试平台,让工程师能够像在软件仿真中一样,对硬件深处的信号进行“上帝视角”般的观测,彻底解决了大规模系统调试难的顽疾。能够与思尔芯的软件仿真芯神驰、硬件仿真芯神鼎和原型验证芯神瞳等灵活衔接,深度融合,大幅提升验证效率。

结语:做中国数字芯片设计的“全能辅助”

纵观全球EDA产业的发展史,巨头的诞生无一不是通过“点工具”的突破,进而走向“全流程”的整合。思尔芯的发展路径,正是这一规律的生动写照。

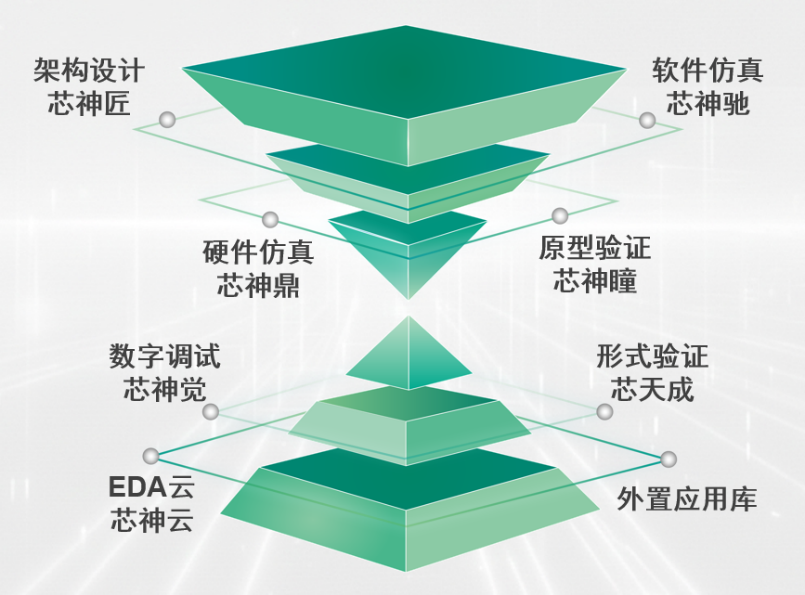

从早期的原型验证单点突围,到如今构建起包含架构设计(芯神匠)、软件仿真(芯神驰)、硬件仿真(芯神鼎)、原型验证(芯神瞳)、形式验证以及数字调试(芯神觉)与云服务(芯神云)的完整闭环,思尔芯已经不再是一家单纯的工具厂商。

特别是在RCF与ICF等底层技术的加持下,思尔芯用“上百颗FPGA级联”和“零故障运行”的硬核数据,证明了其工具链在超大规模设计中的高扩展性与工程化落地能力。它不仅解决了“能不能验证”的问题,更通过分钟级的增量编译,解决了“如何高效验证”的行业痛点。

思尔芯数字EDA产品矩阵

对于中国芯片产业而言,思尔芯提供了一个自主可控、技术闭环的数字设计底座。在“验证即设计”的未来,思尔芯正在用其全流程的布局,辅助每一颗中国芯,以更快的速度、更高的质量,跨越从概念到量产的鸿沟。

END